V1.1

北京智能芯片科技有限公司

FII-PE7030硬件参考指南

文档版本控制

| 文档版本 | 日期 | 修改内容记录 |

| V1.0 | 2019/8/27 | 创建文档 |

| V1.1 | 2019/11/19 | 修改SD卡和可调变阻器部分 |

版权声明:

本手册版权归属北京智能芯片科技有限公司所有, 并保留一切权力。非经本公司(书面形式)同意,任何单位及个人不得擅自摘录或修改本手册部分或全部内容,违者我们将追究其法律责任。

感谢您购买智能芯片科技开发板,在使用产品之前,请仔细地阅读该手册并且确保知道如何正确使用该产品,不合理的操作可能会损坏开发板,使用过程中随时参考该手册以确保正确使用。此手册不断更新中,建议您使用时下载最新版本。

http://www.icintelligent.com

官方淘宝网店:

https://shop296232497.taobao.com

目录

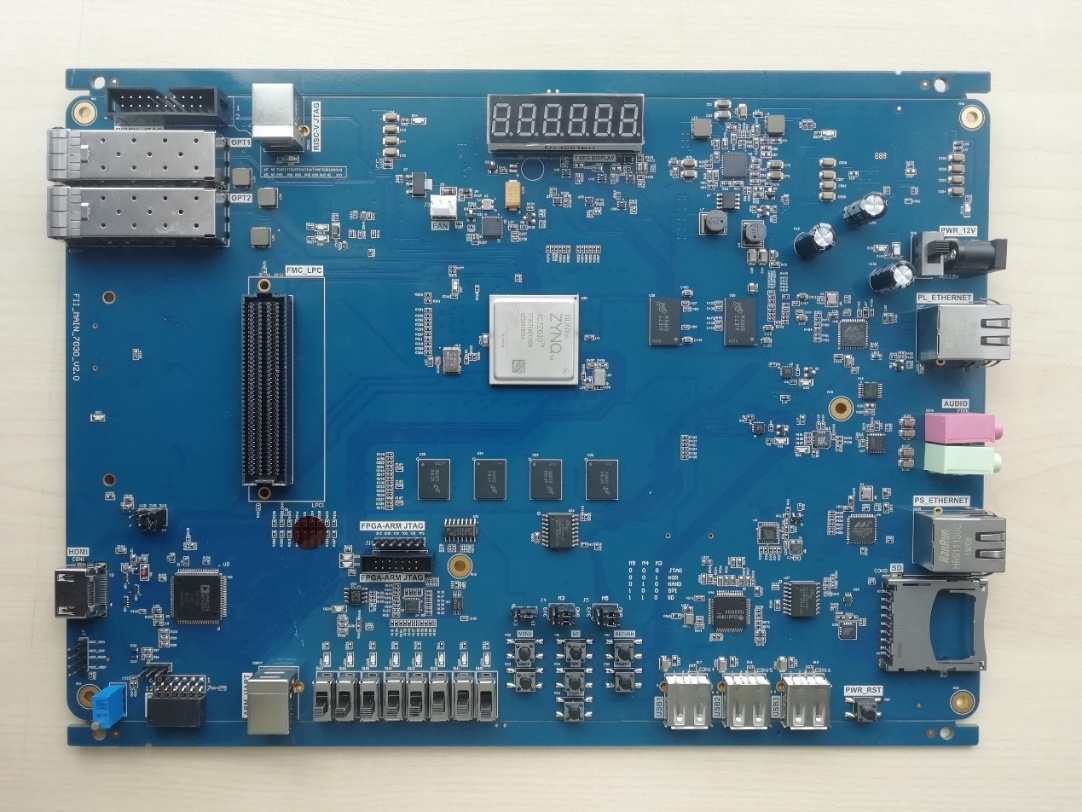

北京智能芯片科技基于 Xilinx ZYNQ7000系列的开发平台,FII-PE7030, 于2018年发布,它是一款Xilinx的ZYNQ7000 SOC芯片的解决方案。它采用ARM+FPGA SOC技术,将双核ARM Cortex-A9和FPGA可编程逻辑集成在一颗芯片上。此款开发平台采用的是Zynq7000系列的XC7Z030-2FFG676I作为核心,同时在ARM和FPGA 上分别具有丰富的硬件资源和外围接口。此款开发板功能强大、资源丰富、速度快,是学习和工程研究理想的平台。设计上我们坚持“实用、精致、可扩展”的设计理念,这也造就了它不但适合于软件工作人员的前期的软件验证,也适合于硬件开发人员的硬件设计即软硬件的系统协作,有助于加快项目的开发进程。

FII-PE7030是一个随时可用的教育平台,其设计涵盖了FPGA开发和实验、ARM SOC开发和实验、网络(铜缆或光纤)开发、数字通信和SDR(软件定义无线电),以及FII-BD9361插件。它是为大学生、教师和其他专业人士设计。FII-PE7030是一个非常灵活的处理平台,能够适应您的项目需要。工程师们成功地将RISC-V(RV32G)和RV64I移植到这个平台上,它成为一个真正的RISC-V SOC平台。

PE7030开发板全貌

一、简介

此款开发板使用的是Xilinx公司的zynq7000系列芯片,型号为XC7Z030-2FFG676I,676个引脚的FBGA封装。这颗芯片可分成处理器部分PS(Processor System) 和可编程逻辑部分PL(Programmable Logic)。在PE7030开发板上,XC7Z030的PS和PL部分都分配了丰富的外部接口和设备,方便用户的使用和功能验证。

此外,一如北京智芯既往,在开发板上集成了USB Cable下载器电路,用户只需要用一个USB线就可以对开发板进行下载和调试。

硬件资源:

- 两片 DDR3(PS 端)四片 DDR3(PL 端),型号为MT41J256M16HA-125.

- 1个200MHz有源晶振,一个可编程晶振,一个33.3333MHz晶振,为开发板提供稳定时钟源;

- 6位共阳极数码管,通过动态扫描实现数据的显示;

- 1路HDMI接口,可以实现彩色图片或摄像头视频的显示;

- 1片I2C接口的EEPROM芯片,型号 M24C08;

- 2个自适应十兆/百兆/千兆以太网接口,PS,PL端各一个;

- 8个独立按键,7个为可编程按键,1个复位按键;

- 1个可调电阻通过它可模拟电压变化;

- 8个独立拨动开关;

- 8位LED发光二极管;

- 1 个 12 脚 GPIO 连接口,符合 PMOD 接口标准;

- 1片32M 串行Flash芯片;

- 3个JTAG接口,2个为FPGA与ARM调试接口,1个为RISC-V CPU 的JTAG调试接口。内置RISC-V CPU 软件调试器,无需外接RISC-V JTAG仿真器;

- 1路UART异步串行接口;

- 音频输入接口(绿色)音频输出接口(红色);

- 4个USB接口,1个为键鼠接口,2个为通用串行接口;

- 1个 USB (USB-B接口)转UART接口,可实现串口通信;

- 一对万兆光纤接口;

- 1个SDcard卡座用于存储操作系统镜像和文件系统;

- 1个LPC接口;

二、认识PE7030

本篇所引用的原理图,为明确主题,突出重点,与主题不相干的电路(如保护电路或滤波电路等)会有忽略或调整,敬请留意。原始资料请参阅附赠的原理图。

前面已经介绍过了,此款开发板FPGA型号为XC7Z030-2FFG676I,是Xilinx一款高性能FPGA.

图2-1 FPGA实物图

芯片资源:

| Resource | Device |

| XC7Z030-2FFG676I | |

| Logic Cells | 125K |

| Look-Up Tables | 78,600 |

| Flip-Flops | 157,200 |

| Block RAM | 9.3Mb |

| DSP Slices | 400 |

| Peak DSP Performance | 593GMACs |

| PCI Express | Gen2 x4 |

| Pin Count | 676 |

图2-2 芯片资源

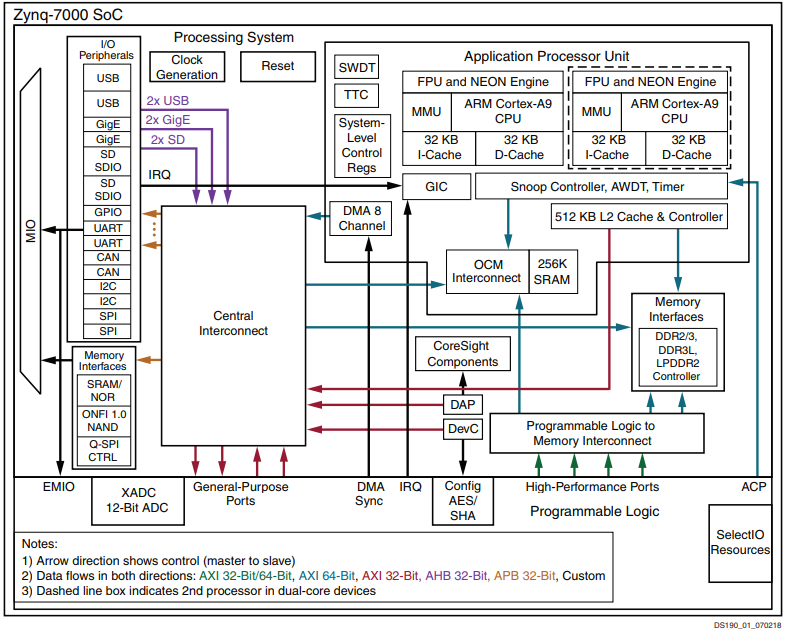

图2-3 ZYNQ芯片总体框图

其中 PS 系统部分的主要参数如下:

– 基于 ARM 双核 CortexA9 的应用处理器, ARM-v7 架构 高达 1GHz

– 每个 CPU 32KB 1 级指令和数据缓存, 512KB 2 级缓存 2 个 CPU 共享

– 片上 boot ROM 和 256KB 片内 RAM

– 外部存储接口, 支持 16/32 bit DDR2、 DDR3 接口

– 两个千兆网卡支持:发散-聚集 DMA , GMII, RGMII, SGMII 接口

– 两个 USB2.0 OTG 接口,每个最多支持 12 节点

– 两个 CAN2.0B 总线接口

– 两个 SD 卡、 SDIO、 MMC 兼容控制器

– 2 个 SPI, 2 个 UARTs, 2 个 I2C 接口

– 4 组 32bit GPIO, 54( 32+22)作为 PS 系统 IO, 64 连接到 PL

– PS 内和 PS 到 PL 的高带宽连接

芯片为 BGA 封装, 676 个引脚,引脚间距为 1.0mm。当我们使用 BGA 封装的芯片以后,引脚名称由“字母+数字”组成,比如C8, E3 等等,因此我们在看原理图的时候,看到的”字母+数字”这种形式的,就是代表了 BGA的引脚。

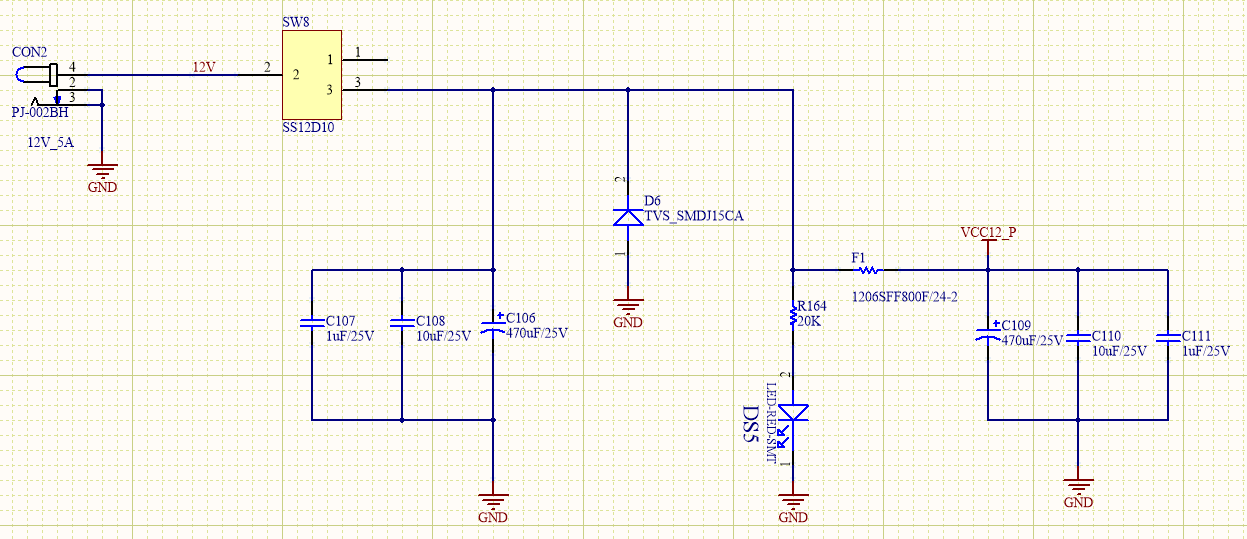

开发板使用12V直流电源供电(请使用开发板自带的电源,不要用其他规格的电源,以免损坏开发板)。其供电接口如下:

图2-3供电接口实物图

图2-4 原理图供电部分

U47

U4

VCC12

开关

RT7259

RT7259

5V

U48

1.5V

RT7259

5V

RT7259

U5

3.3V

RT8068

U53

2.5V

图2-5 原理图电源部分

开发板输入12V DC电源,经过2片RT7259转化成5V电源。再经过U4、U5、U53转换成1.5V,3.3V,2.5V,在经过其他电路转换成需要的1.0V,1.8V等等(详细资料请参看设计原理图)。

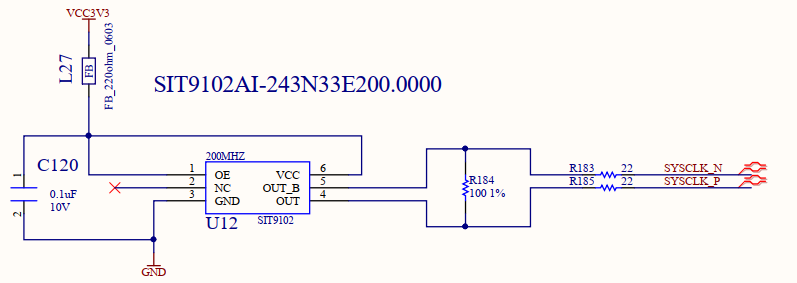

板载3片有源晶振,一片为200MHz,一片默认为156.25MHz的可编程晶振(si570)。另一片是PS端使用的33.3333MHz晶振。原理图如下:

图3-1 原理图晶振部分

图3-2 可编程晶振原理图部分

图3-3 33.3333M晶振原理图部分

实物图:

图3-4 晶振实物图

引脚分配

| 引脚名称 | FPGA引脚 |

| CLK_200M_P | AC13 |

| CLK_200M_N | AD13 |

| USRCLK_P | AD20 |

| USRCLK_N | AD21 |

| PS_CLK | B24 |

图4-1 六位数码管实物图

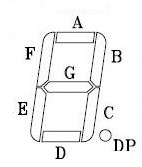

数码管是一种是半导体发光器件,数码管可分为七段数码管和八段数码管,区别在于八段数码管比七段数码管多一个用于显示小数点的发光二极管单元DP(decimal point),其基本单元是发光二极管。数码管的段结构如下图所示:

图4-2 数码管的段结构

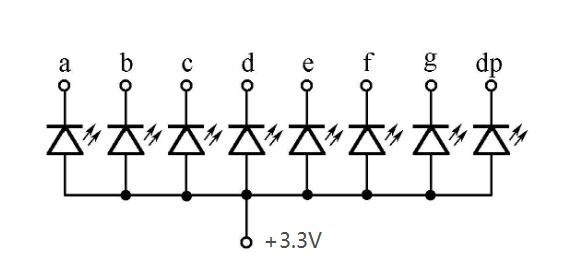

我们使用的是共阳极数码管,共阳极顾名思义,就是将发光二极管的阳极连接在一起。

图4-3 共阳极数码管原理图

为了点亮8段LED管的某一段,就需要把相应引脚的电平拉低;当引脚置为高电平时,相应的字段就不会点亮。本开发板上采用的是6位一体的八段数码管,其原理图如下图所示:

图4-4 原理图数码管部分

六位一体数码管是属于动态显示,由于人的视觉暂留现象及发光二极管的余辉效应,尽管实际上各位数码管并非同时点亮,但只要扫描的速度足够快,给人的印象就是一组稳定的显示数据,不会有闪烁感。六位一体数码管的相同的段都接在了一起,一共是 8 个引脚,然后加上 6个控制信号引脚,一共是 14 个引脚,如图 4-4 所示。其中 SEG_PA、SEG_PB、SEG_PC、SEG_PD、SEG_PE、SEG_PF、SEG_PG、SEG_DP对应数码管的 A,B,C,D,E,F,G, DP; SEG_3V3_D[0..5]是六个数码管的六个控制引脚,也是低电平有效,当控制引脚为低电平时,对应的数码管有了供电电压,这样数码管才能点亮,否则无论数码管的段如何变化,也不能点亮对应的数码管。

数码管引脚分配

| 引脚名称 | FPGA引脚 | 说明 |

| SEG PA | J10 | 段A |

| SEG PB | J9 | 段B |

| SEG PC | A7 | 段C |

| SEG PD | B7 | 段D |

| SEG PE | A8 | 段E |

| SEG PF | A9 | 段F |

| SEG PG | A10 | 段G |

| SEG DP | B10 | 段DP |

| SEG_D0_3V3 | C1 | 右边数第一个数码管 |

| SEG_D1_3V3 | E3 | 右边数第二个数码管 |

| SEG_D2_3V3 | F7 | 右边数第三个数码管 |

| SEG_D3_3V3 | D6 | 右边数第四个数码管 |

| SEG_D4_3V3 | H11 | 右边数第五个数码管 |

| SEG_D5_3V3 | J11 | 右边数第六个数码管 |

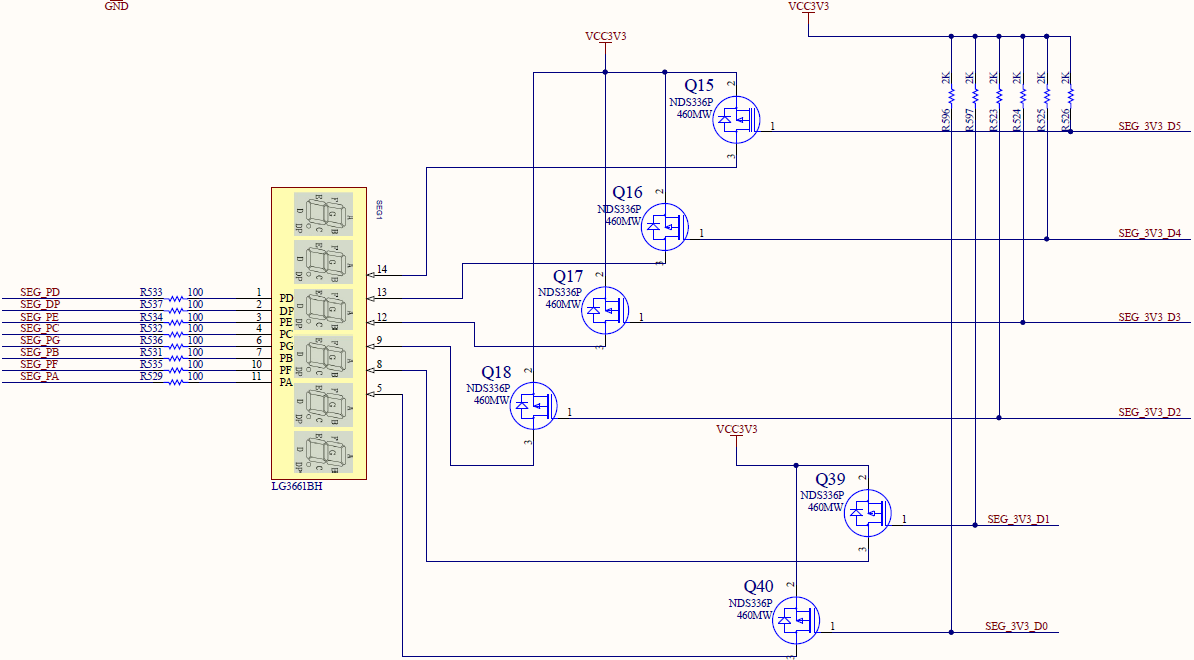

图像显示处理一直是FPGA研究的重点内容。现阶段图像显示方式也在不断发展。图像显示接口也逐渐由旧的VGA接口向新的DVI或者HDMI接口的方式过渡。HDMI是高清多媒体接口(High Definition Multimedia Interface)的简称。是一种数字化视频/音频接口技术,适合影像传输的专用型数字化接口,可同时传送音频和影像信号。

ADV7511是一款可以将fpga信号转化为HDMI时序的芯片。具体内容可以查看相关芯片手册。其中ADV7511_Programming_Guide和ADV7511_Hardware_Users_Guide是最重要的,可以通过查看该文档,来对ADV7511的寄存器进行配置。

此芯片通信地址由PD引脚来选择,可为0x72或0x7A,本开发板PD引脚接地,因此通信地址是0x72。

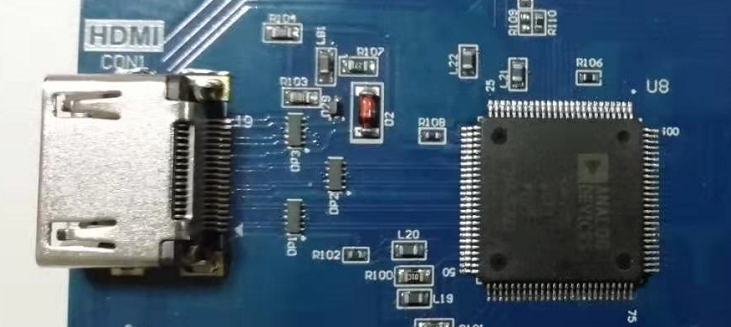

图5-1 HDMI接口与ADV7511芯片实物图

HDMI引脚分配

| 信号名称 | 引脚名称 | FPGA引脚 |

| HDMI_INT | INT | W20 |

| HDMI_VSYNC | VSYNC | AE18 |

| HDMI_HSYNC | HSYNC | AA22 |

| HDMI_CLK | CLK | AD19 |

| HDMI_D23 | D35 | AB22 |

| HDMI_D22 | D34 | W19 |

| HDMI_D21 | D33 | AA24 |

| HDMI_D20 | D32 | AB20 |

| HDMI_D19 | D31 | AB21 |

| HDMI_D18 | D30 | AA19 |

| HDMI_D17 | D29 | AB24 |

| HDMI_D16 | D28 | AB19 |

| HDMI_D15 | D23 | AF25 |

| HDMI_D14 | D22 | AC19 |

| HDMI_D13 | D21 | AA23 |

| HDMI_D12 | D20 | AE20 |

| HDMI_D11 | D19 | AD23 |

| HDMI_D10 | D18 | AF20 |

| HDMI_D9 | D17 | AD26 |

| HDMI_D8 | D16 | AF24 |

| HDMI_D7 | D11 | AF19 |

| HDMI_D6 | D10 | AD25 |

| HDMI_D5 | D9 | AC22 |

| HDMI_D4 | D8 | AE23 |

| HDMI_D3 | D7 | AC21 |

| HDMI_D2 | D6 | AE26 |

| HDMI_D1 | D5 | AC18 |

| HDMI_D0 | D4 | AD18 |

| HDMI_DE | DE | AE25 |

| HDMI_I2S3 | SPDIF | AE21 |

| HDMI_MCLK | MCLK | Y20 |

| HDMI_I2S0 | I2S0 | AF23 |

| HDMI_I2S1 | I2S1 | AF22 |

| HDMI_I2S2 | I2S2 | AF18 |

| HDMI_I2S3 | I2S3 | AE21 |

| HDMI_SCLK | SCLK | W18 |

| HDMI_LRCLK | LRCLK | Y18 |

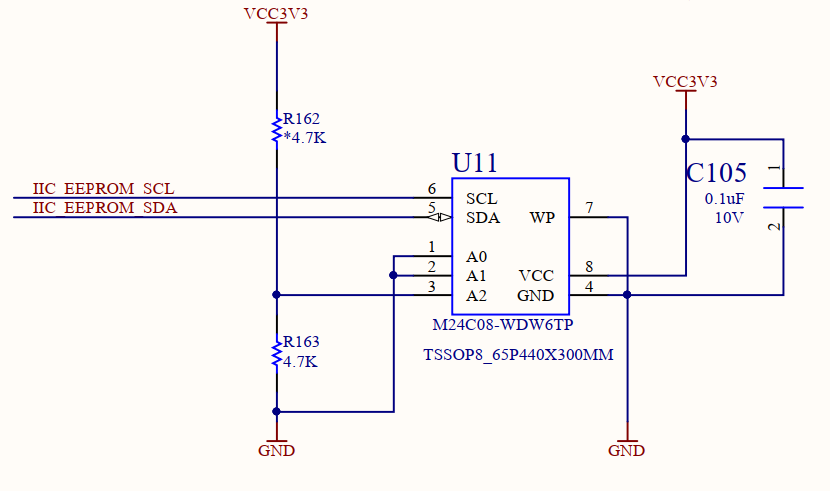

EEPROM 一般用在仪器仪表等设计上,常用作一些参数的存储,掉电不丢失,操作简单,是非常理想的存储器件。

开发板板载了一片 EEPROM,型号为 M24C08,容量为1KByte(1024*8bit),通过 IIC 总线进行通信。

IIC(Inter-Integrated Circuit)字面上的意思是集成电路之间,它其实是IIC Bus简称,所以中文应该叫集成电路总线,它是一种串行通信总线,使用多主从架构,由飞利浦公司在1980年代为了让主板、嵌入式系统或手机用以连接低速周边设备而发展。也写为“I²C”、“I2C”,正确读法为“I方C”(”I-squared-C”)。

图 6-1 为 EEPROM 的原理图

图6-1 原理图EEPROM部分

可以看到芯片的地址线A2、A1、A0都连接了GND,故芯片的通信地址是7’B1010000(此芯片前四位地址为固定的1010)。图6-2为实物图

图6-2 EEPROM实物图

这颗芯片通过PCA9548连接到I2CMain总线,再连接到FPGA。

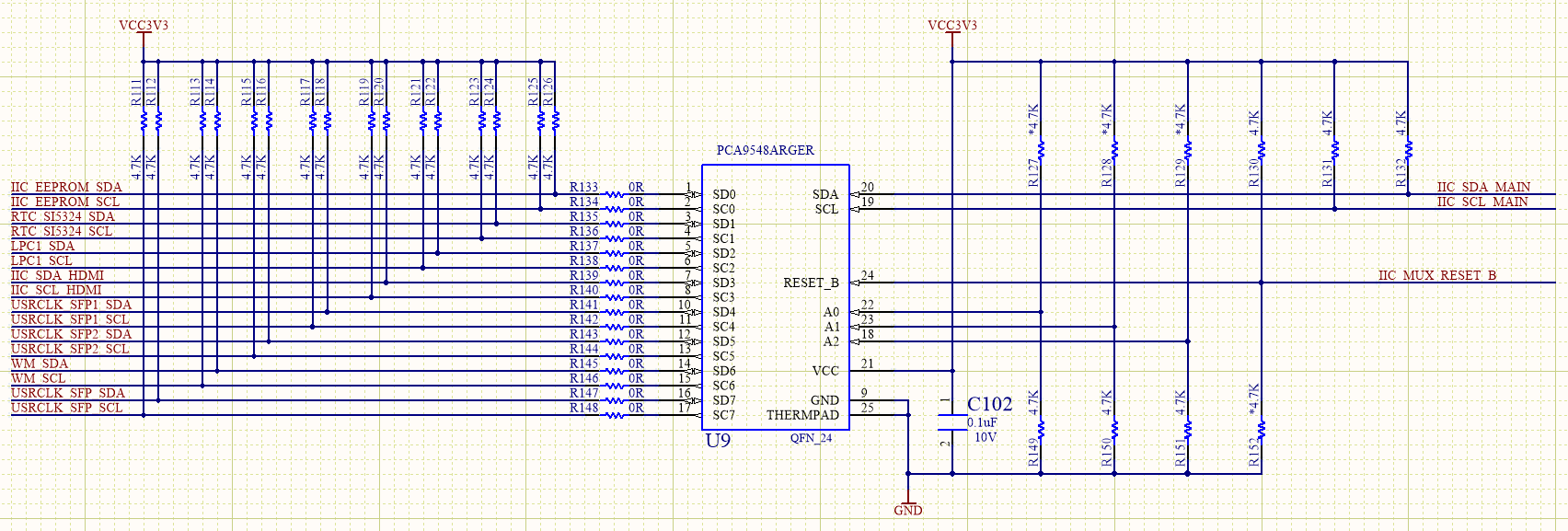

PCA9548是NXP公司生产的I2C总线扩展器件,通过它可以将1路I2C总线扩展为8路。在对内部控制寄存器进行相应的配置后,可以同事选择1路或多路下行I2C与上行I2C总线连接。通过外部的硬件复位可使器件恢复到默认状态——断开上下行总线之间的连接,提高系统的可靠性。每个I2C接口和中断输入输出均为开漏,所有I/O口都可以承受5V的输入电压。设计原理图如下:

图6-3 PCA9548 I2C总线扩展原理图部分

EEPROM引脚分配

| M24C08引脚 | PCA9548引脚 | FPGA引脚 |

| SDA | 1 | W17 |

| SCL | 2 | W14 |

以太网作为目前最为常用的数据通信方式,相信大家对它再熟悉不过了,在我们日常生活中,可以说它无处不在。以太网从最初的10Mb/s,到后来的100Mb/s再到1000Mb/s,其速度越来越快。

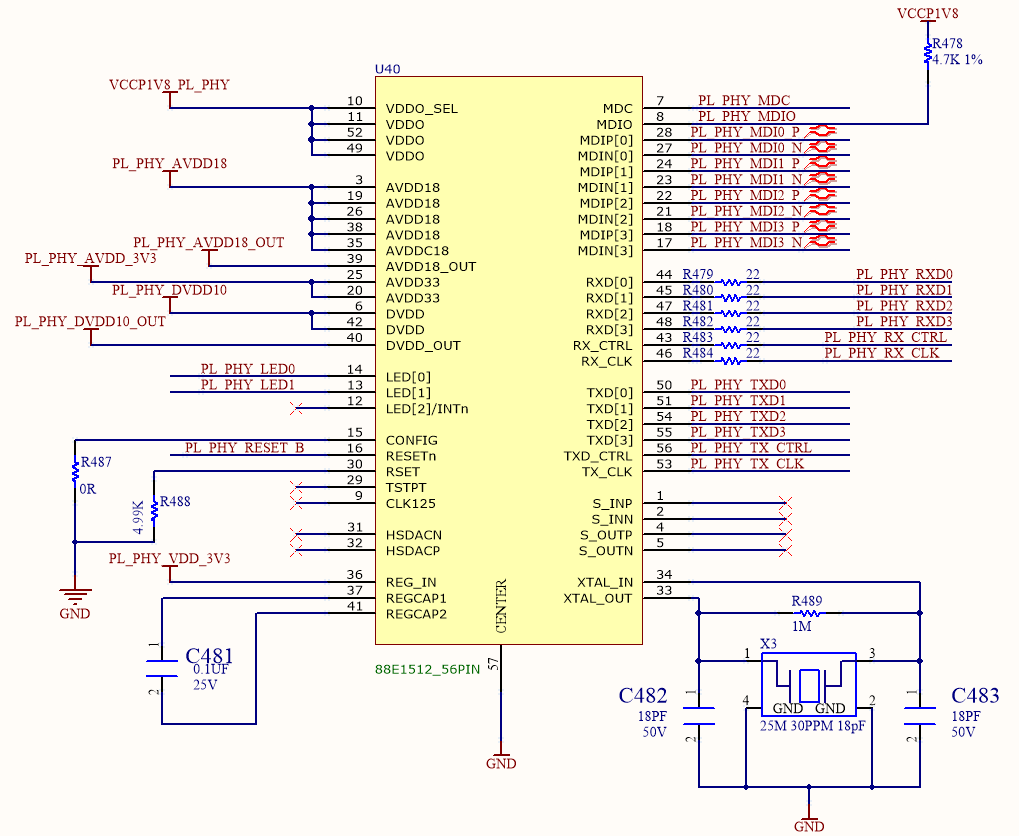

PE7030开发板搭载了一颗88E1512千兆以太网芯片。88E1512是Marvell推出的一款高集成的网络接收PHY芯片,它符合10Base-T,100Base-TX和1000Base-T IEEE802.3标准,可以通过CAT 5 UTP电缆及CAT 3 UTP电缆传输网络数据,该芯片在网络通信中属于物理层,用于MAC与PHY之间的数据通信。主要应用于网络接口适配器,网络集线器,网关以及一些嵌入式设备当中。

88E1512的主要功能特性包括:

1、符合1000Base-T IEEE802.3ab标准

2、符合100Base-TX IEEE802.3u标准

3、符合10Base-T IEEE802.3标准

4、支持IEEE 802.3 RGMII接口

5、支持IEEE 802.3 GMII、MII接口

6、支持网络唤醒功能

7、支持中断功能

8、支持交叉检测及自动校正

9、支持半双工、全双工操作

10、1000M通信用CAT 5网线可达到100m

11、RGMII接口可支持3.3V、2.5V、1.8V、1.5V信号

12、可提供三种网络状态的LED指示

其原理图如下:

图7-1 原理图中千兆网芯片部分

图7-2为实物图

图7-2千兆网实物图

千兆网引脚分配

| 88E1512引脚 | 信号名称 | FPGA引脚 |

| MDC | PL_PHY_MDC | K8 |

| MDIO | PL_PHY_MDIO | K7 |

| RXD[0] | PL_PHY_RXD0 | K3 |

| RXD[1] | PL_PHY_RXD1 | K1 |

| RXD[2] | PL_PHY_RXD2 | H2 |

| RXD[3] | PL_PHY_RXD3 | G1 |

| RX_CTRL | PL_PHY_RX_CTRL | L3 |

| RX_CLK | PL_PHY_RX_CLK | J4 |

| TXD[0] | PL_PHY_TXD0 | M2 |

| TXD[1] | PL_PHY_TXD1 | L2 |

| TXD[2] | PL_PHY_TXD2 | L4 |

| TXD[3] | PL_PHY_TXD3 | L5 |

| TXD_CTRL | PL_PHY_TX_CTRL | K5 |

| TX_CLK | PL_PHY_TX_CLK | N3 |

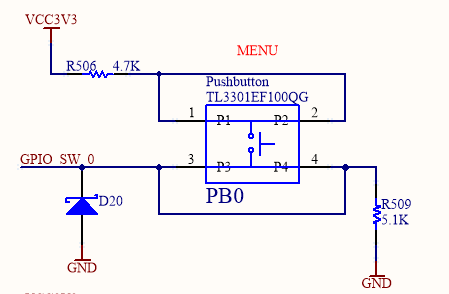

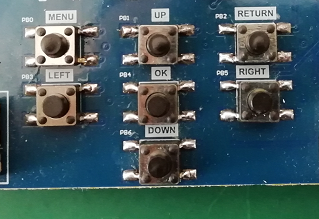

板载按键为常见的轻触按键,按下有效,松开后自动弹起。共8个,分别为PB0(MENU)PB1(UP),PB2(RETURN),PB3(LETF),PB4(OK),PB5(RIGHT),PB6(DOWN)和一个硬件复位按键RESET。默认为低电平,按下为高电平。原理图如图8-1

图8-1 原理图按键部分(MENU按键)

实物图如图8-2:

图8-2 按键实物图

按键引脚分配

| 引脚名称 | FPGA引脚 |

| MENU | L19 |

| UP | G4 |

| RETURN | F4 |

| LEFT | D4 |

| OK | D3 |

| RIGHT | F2 |

| DOWN | G2 |

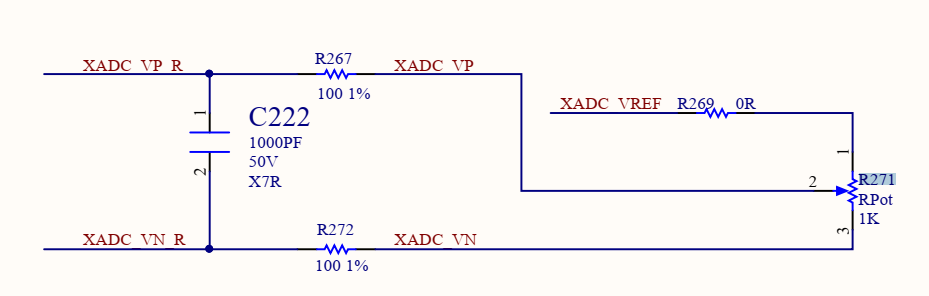

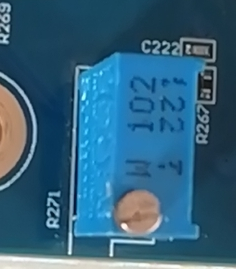

板载一片普通旋钮可调变阻器,阻值范围0~1K欧姆。可调变阻器连接于PS端的ADC部分,可直读取其数值。主要用于学习SoC的ADC功能。原理图如下:

图9-1 原理图可调变阻器部分

实物图如图9-2:

图9-2 可调变阻器实物图

引脚分配

| 变阻器引脚 | 网络名 | ARM引脚 | ARM引脚名称 |

| 1 | XADC_VREF | P14 | VREFP_0 |

| 2 | XADC_VP_R | N14 | VP_0 |

| 3 | XADC_VN_R | P13 | VN_0 |

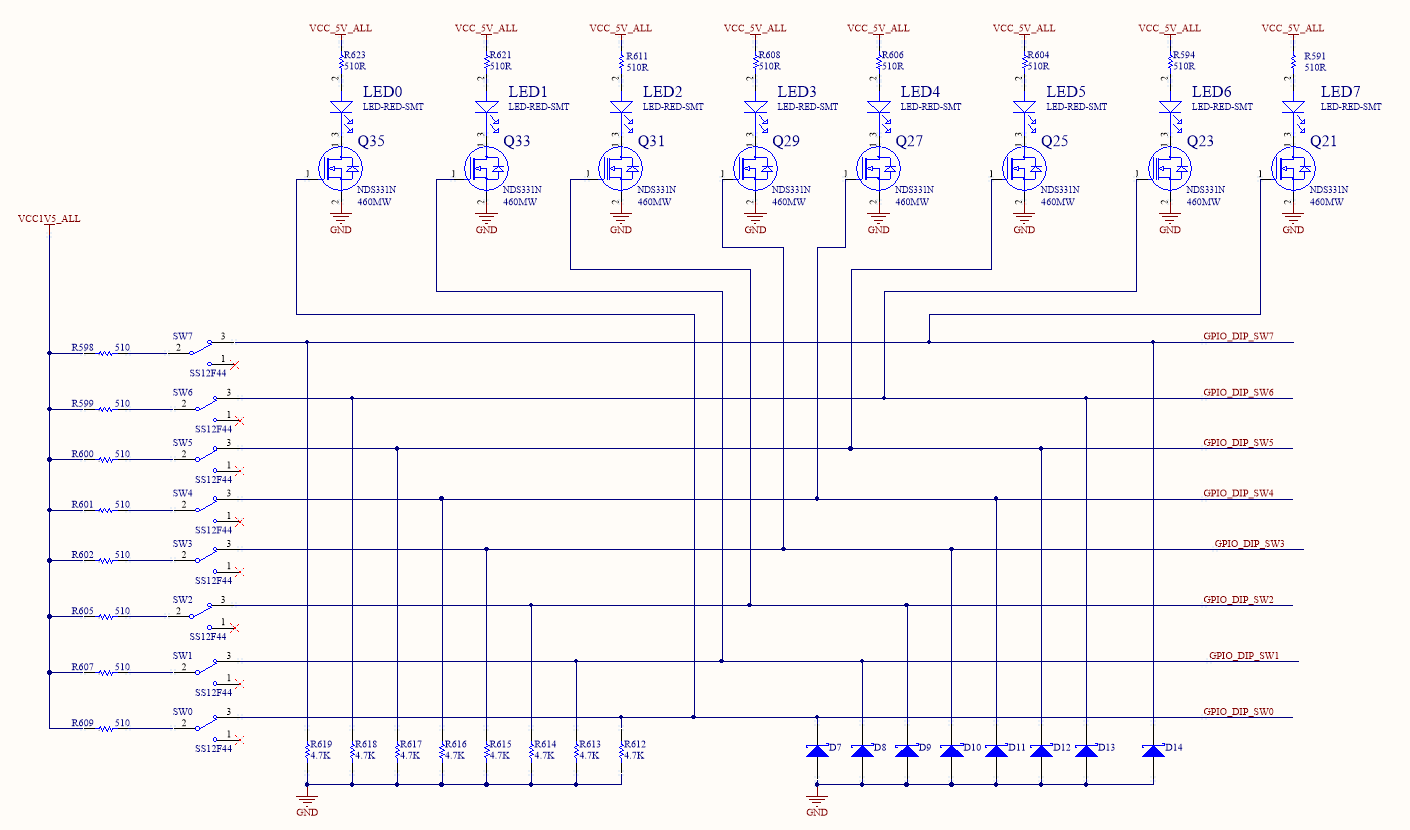

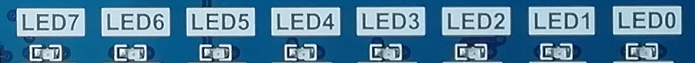

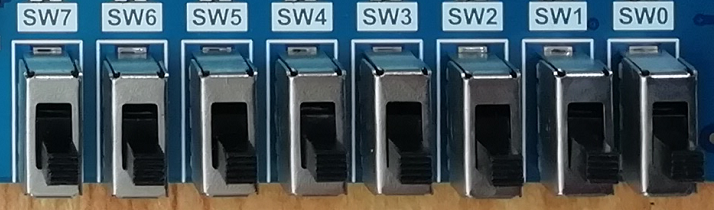

板载了8位拨动开关与8个LED,当拨动开关导通时,FPGA管脚得到高电平,如果FPGA不控制,则对应的LED会亮。其原理图如下:

图10-1 原理图拨码开关部分

实物图如图10-2所示

图10-2 拨码开关与LED实物图

拨动开关引脚分配

| 引脚名称 | FPGA引脚 |

| SW0,LED0 | A17 |

| SW1,LED1 | E8 |

| SW2,LED2 | C6 |

| SW3,LED3 | B9 |

| SW4,LED4 | B6 |

| SW5,LED5 | H6 |

| SW6,LED6 | H7 |

| SW7,LED7 | G9 |

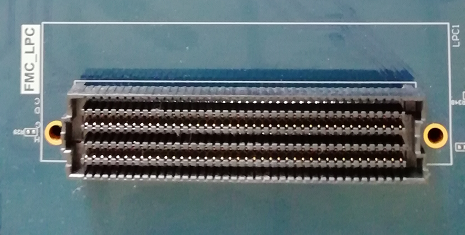

板载一片FMC-LPC端口,是一片板间高速连接器,符合VITA57标准, ASP系列, 有160个触点的插座,插座触点之间的间距是1.27mm,共4排针脚。

实物图如图11-1

图11-1 FMC-LPC实物图

FMC-LPC引脚分配

| LPC引脚(信号名) | 网络名 | FPGA引脚 |

| C2 (DP0_C2M_P) | FMC_MGT_RX_P | AB4 |

| C3 (DP0_C2M_N) | FMC_MGT_RX_N | AB3 |

| C6 (DP0_M2C_P) | FMC_MGT_TX_P | AA2 |

| C7 (DP0_M2C_N) | FMC_MGT_TX_N | AA1 |

| C10 (LA06_P) | NetLPC1_C10 | AB15 |

| C11 (LA06_N) | NetLPC1_C11 | AB14 |

| C14 (LA10_P) | LPC1_TX_D3_P | AF15 |

| C15 (LA10_N) | LPC1_TX_D3_N | AF14 |

| C18 (LA14_P) | LPC1_TX_D4_P | AD16 |

| C19 (LA14_N) | LPC1_TX_D4_N | AD15 |

| C26 (LA27_P) | LPC1_SPI_DI | AA12 |

| C27 (LA27_N) | LPC1_SPI_DO | Y13 |

| D8 (LA01_P_CC) | NetLPC1_D8 | AB17 |

| D9 (LA01_N_CC) | NetLPC1_D9 | AB16 |

| D11 (LA05_P) | NetLPC1_D11 | W16 |

| D12 (LA05_N) | NetLPC1_D12 | W15 |

| D14 (LA09_P) | LPC1_TX_FRAME_P | AE13 |

| D15 (LA09_N) | LPC1_TX_FRAME_N | AF13 |

| D17 (LA13_P) | LPC1_TX_D2_P | Y17 |

| D18 (LA13_N) | LPC1_TX_D2_N | AA17 |

| D23 (LA23_P) | LPC1_CTRL_OUT6 | J6 |

| D24 (LA23_N) | LPC1_CTRL_OUT7 | N7 |

| D26 (LA26_P) | LPC1_SPI_ENB | AA133 |

| D27 (LA26_N) | LPC1_SPI_CLK | W13 |

| G2 (CLK1_M2C_P) | FMC_MGT_CLK_P | U6 |

| G3 (CLK1_M2C_N) | FMC_MGT_CLK_N | U5 |

| G6 (LA00_P_CC) | LPC1_DATA_CLK_P | AC14 |

| G7 (LA00_N_CC) | LPC1_DATA_CLK_N | AD1 |

| G9 (LA03_P) | NetLPC1_G9 | AE17 |

| G10 (LA03_N) | NetLPC1_G10 | AF17 |

| G12 (LA08_P) | LPC1_FB_CLK_P | AE12 |

| G13 (LA08_N) | LPC1_FB_CLK_N | AF12 |

| G15 (LA12_P) | LPC1_TX_D1_P | AE16 |

| G16 (LA12_N) | LPC1_TX_D1_N | AE15 |

| G18 (LA16_P) | LPC1_ENABLE | AB10 |

| G19 (LA16_N) | LPC1_TXNRX | Y11 |

| G21 (LA20_P) | LPC1_CTRL_OUT0 | AB11 |

| G22 (LA20_N) | LPC1_CTRL_OUT1 | Y12 |

| G24 (LA22_P) | LPC1_CTRL_OUT4 | N1 |

| G25 (LA22_N) | LPC1_CTRL_OUT5 | M1 |

| G27 (LA25_P) | NetLPC1_G27 | N4 |

| G28 (LA25_N) | NetLPC1_G28 | M4 |

| H4 (CLK0_M2C_P) | LPC1_CLK_OUT | AD11 |

| H7 (LA02_P) | NetLPC1_H7 | AC17 |

| H8 (LA02_N) | NetLPC1_H8 | AC16 |

| H10 (LA04_P) | NetLPC1_H10 | AA15 |

| H11 (LA04_N) | NetLPC1_H11 | AA1 |

| H13 (LA07_P) | NetLPC1_H13 | Y16 |

| H14 (LA07_N) | NetLPC1_H14 | Y15 |

| H16 (LA11_P) | LPC1_TX_D0_P | AE11 |

| H17 (LA11_N) | LPC1_TX_D0_N | AF10 |

| H19 (LA15_P) | LPC1_TX_D5_P | AE10 |

| H20 (LA15_N) | LPC1_TX_D5_N | AD10 |

| H22 (LA19_P) | LPC1_EN_AGC | AC11 |

| H23 (LA19_N) | NetLPC1_H23 | AC12 |

| H25 (LA21_P) | LPC1_CTRL_OUT2 | AA10 |

| H26 (LA21_N) | LPC1_CTRL_OUT3 | AB12 |

| H28 (LA24_P) | NetLPC1_H28 | H3 |

| H29 (LA24_N) | NetLPC1_H29 | K2 |

| H31 (LA28_P) | LPC1_RESETB | Y10 |

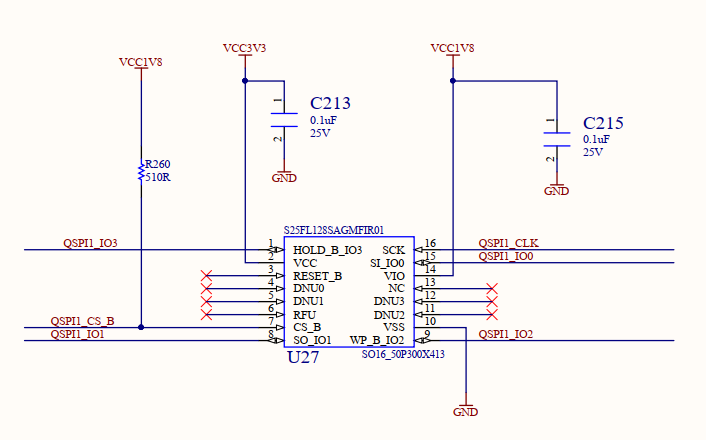

S25FL128SAGMFIR01是一个串行FLASH芯片,容量为128Mbit,对于存储FPGA中的程序来说,这个容量绰绰有余。图12-1为S25FL128SAGMFIR01在原理图中的部分。

图12-1 原理图FLASH部分

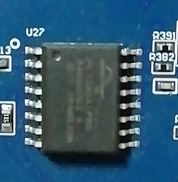

实物图如图12-2

图12-2 FLASH芯片实物图

引脚分配

| FLASH引脚 | 信号名 | FPGA引脚 |

| HOLD_B_I03 | QSPI1_IO3 | N6 |

| CS_B | QSPI1_SC_B | N8 |

| SO_IO1 | QSPI1_IO1 | M7 |

| SCK | QSPI1_CLK | D1 |

| SI_IO0 | QSPI1_IO0 | J3 |

| WP_B_IO2 | QSPI1_IO2 | K6 |

开发板留有1个GPIO接口。含有6路标准IO引脚的PFGA资源,2个GND信号,2个电源可调节(3.3V,5V)针脚。原理图如下:

图13-1 原理图GPIO部分

实物图如图13-2所示

图13-2 GPIO实物图

GPIO引脚分配

| 引脚名称 | FPGA引脚 | 说明 |

| P1-1 | E1 | 标准IO |

| P1-2 | F3 | 标准IO |

| P1-3 | E2 | 标准IO |

| P1-4 | J1 | 标准IO |

| P1-5 | GND | |

| P1-6 | VCC | |

| P1-7 | NULL | |

| P1-8 | NULL | |

| P1-9 | H11 | 标准IO |

| P1-10 | H4 | 标准IO |

| P1-11 | GND | |

| P1-12 | VCC |

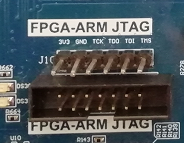

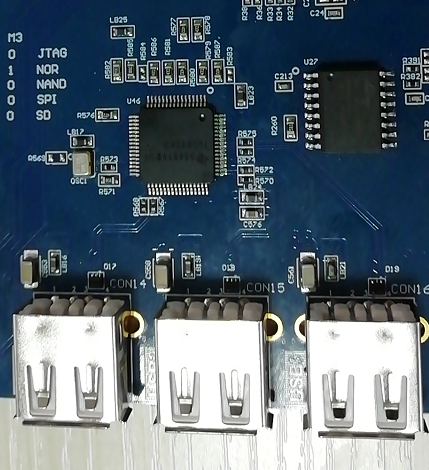

开发板为FPGA下载提供2个JTAG接口,分别是J10(2.54mm间距排针)和J8(2.00mm牛角座)。JTAG原理如图14-1所示:

图14-1 原理图JTAG接口部分

实物图如图14-2所示

图14-2 JTAG接口实物图

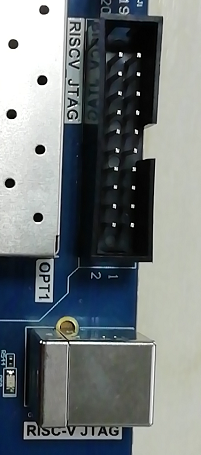

RISC-V下载接口也有两个,如下图所示。可为RISC-V CPU下载程序。实物与管脚分配如下:

图14-3 RISC-V下载接口实物图

RISC-V下载接口引脚分配

| 网络名 | J1针脚 | FPGA引脚 |

| RISCV_n | 3 | V19 |

| RISCV_TTDI | 5 | AA25 |

| RISCV_TTMS | 7 | AB26 |

| RISCV_TTCK | 9 | AC23 |

| RISCV_TRTCK | 11 | AC23 |

| RISCV_TTDO | 13 | AB25 |

| RISCV_TSRST_n | 15 | AD24 |

板载两个USB-B接口和两片FT2232芯片,用于FPGA或CPU程序下载之外,还可用于串行数据通信。

原理图请参阅设计图纸,实物图如下:

图15-2 USB-B接口与CP2102芯片实物图

UART引脚分配

| 引脚名称 | FPGA引脚 |

| (RISC-V JTAG)TX | AC26 |

| (RISC-V JTAG)RX | AE22 |

| (ARM-UART)TX | B22 |

| (ARM-UART)RX | B20 |

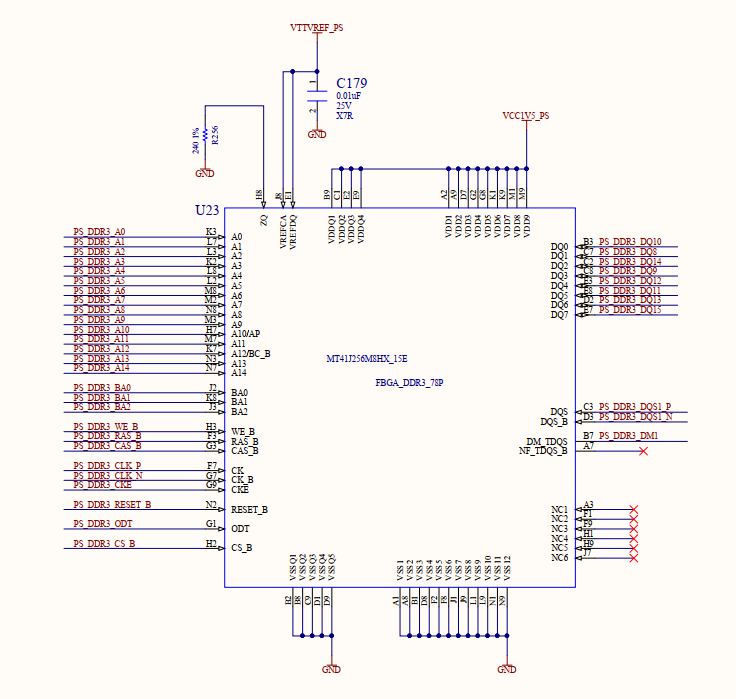

DDR3全称DDR3 SDRAM(同步动态随机存取内存(synchronous dynamic random-access memory,简称SDRAM)),是一种内存规格。与SRAM相比,动态随机存取存储器(DRAM)里面所储存的数据需要周期性地更新。开发板载有六片DDR3,其中PS端4片,容量分别为256M * 8bit,PL端2片,容量分别为256M*16bit。部分设计原理图如下(完整资料请参阅设计原理图):

图16-1 原理图DDR3部分

实物图如下:

图16-2 DDR3实物图

引脚分配:

| DDR3引脚(信号名) | 网络名 | FPGA引脚 |

| U38-A2 (PL_DDR_DQ13) | DQ13 | G16 |

| U38-A3 (PL_DDR_DQ15) | DQ15 | G14 |

| U38-A7 (PL_DDR_DQ12) | DQ12 | H13 |

| U38-B7 (PL_DDR_DQS1_N) | UDQS# | J15 |

| U38-B8 (PL_DDR_DQ14) | DQ14 | H12 |

| U38-C2 (PL_DDR_DQ11) | DQ11 | J14 |

| U38-C3 (PL_DDR_DQ9) | DQ9 | F14 |

| U38-C7 (PL_DDR_DQS1_P) | UDQS | K15 |

| U38-C8 (PL_DDR_DQ10) | DQ10 | J13 |

| U38-D3 (PL_DDR_DM1) | UDM | G15 |

| U38-D7 (PL_DDR_DQ8) | DQ8 | K13 |

| U38-E3 (PL_DDR_DQ0) | DQ0 | E12 |

| U38-E7 (PL_DDR_DM0) | LDM | E11 |

| U38-F2 (PL_DDR_DQ2) | DQ2 | F13 |

| U38-F3 (PL_DDR_DQS0_P) | LDQS | G10 |

| U38-F7 (PL_DDR_DQ1) | DQ1 | D10 |

| U38-F8 (PL_DDR_DQ3) | DQ3 | E10 |

| U38-G2 (PL_DDR_DQ6) | DQ6 | D11 |

| U38-G3 (PL_DDR_DQS0_N) | LDQS# | F10 |

| U38-H1 (VTTVREF_PL) | VREFDQ | C8 |

| U38-H3 (PL_DDR_DQ4) | DQ4 | F12 |

| U38-H7 (PL_DDR_DQ7) | DQ7 | G11 |

| U38-H8 (PL_DDR_DQ5) | DQ5 | G12 |

| U38-J3 (PL_DDR_RAS_N) | RAS# | C9 |

| U38-J7 (PL_DDR_CK_P) | CK | C8 |

| U38-K1 (PL_DDR_DOT0) | ODT | A4 |

| U38-K3 (PL_DDR_CAS_N) | CAS# | A2 |

| U38-K7 (PL_DDR_CK_N) | CK# | C7 |

| U38-K9 (PL_DDR_CKE_0) | CKE | D9 |

| U38-L2 (PL_DDR_CS_N) | CS# | A5 |

| U38-L3 (PL_DDR_WE_N) | WE# | D8 |

| U38-L7 (PL_DDR_A10) | A10/AP | A3 |

| U38-M2 (PL_DDR_BA0) | BA0 | C4 |

| U38-M3 (PL_DDR_BA2) | BA2 | B1 |

| U38-M7 (PL_DDR_A15) | NC | B5 |

| U38-M8 (VTTVREF_PL) | VREFCA | C8 |

| U38-N2 (PL_DDR_A3) | A3 | B4 |

| U38-N3 (PL_DDR_A0) | A0 | E7 |

| U38-N7 (PL_DDR_A12) | A12/BC# | C2 |

| U38-N8 (PL_DDR_BA1) | BA1 | C3 |

| U38-P2 (PL_DDR_A5) | A5 | G7 |

| U38-P3 (PL_DDR_A2) | A2 | D5 |

| U38-P7 (PL_DDR_A1) | A1 | E6 |

| U38-P8 (PL_DDR_A4) | A4 | B2 |

| U38-R2 (PL_DDR_A7) | A7 | F9 |

| U38-R3 (PL_DDR_A9) | A9 | G5 |

| U38-R7 (PL_DDR_A11) | A11 | E5 |

| U38-R8 (PL_DDR_A6) | A6 | F5 |

| U38-T2 (PL_DDR_RST_N) | RESET# | H14 |

| U38-T3 (PL_DDR_A13) | A13 | J8 |

| U38-T7 (PL_DDR_A14) | A14 | F8 |

| U38-T8 (PL_DDR_A8) | A8 | G6 |

| U39-A2 (PL_DDR_DQ13) | DQ13 | C14 |

| U39-A3 (PL_DDR_DQ15) | DQ15 | B14 |

| U39-A7 (PL_DDR_DQ12) | DQ12 | D13 |

| U39-B7 (PL_DDR_DQS1_N) | UDQS# | A14 |

| U39-B8 (PL_DDR_DQ14) | DQ14 | C12 |

| U39-C2 (PL_DDR_DQ11) | DQ11 | C11 |

| U39-C3 (PL_DDR_DQ9) | DQ9 | A13 |

| U39-C7 (PL_DDR_DQS1_P) | UDQS | A15 |

| U39-C8 (PL_DDR_DQ10) | DQ10 | B12 |

| U39-D3 (PL_DDR_DM1) | UDM | B11 |

| U39-D7 (PL_DDR_DQ8) | DQ8 | A12 |

| U39-E3 (PL_DDR_DQ0) | DQ0 | B17 |

| U39-E7 (PL_DDR_DM0) | LDM | B16 |

| U39-F2 (PL_DDR_DQ2) | DQ2 | D16 |

| U39-F3 (PL_DDR_DQS0_P) | LDQS | C17 |

| U39-F7 (PL_DDR_DQ1) | DQ1 | D15 |

| U39-F8 (PL_DDR_DQ3) | DQ3 | D14 |

| U39-G2 (PL_DDR_DQ6) | DQ6 | E16 |

| U39-G3 (PL_DDR_DQS0_N) | LDQS# | C16 |

| U39-H1 (VTTVREF_PL) | VREFDQ | C8 |

| U39-H3 (PL_DDR_DQ4) | DQ4 | F15 |

| U39-H7 (PL_DDR_DQ7) | DQ7 | B15 |

| U39-H8 (PL_DDR_DQ5) | DQ5 | E15 |

| U39-J3 (PL_DDR_RAS_N) | RAS# | C9 |

| U39-J7 (PL_DDR_CK_P) | CK | C8 |

| U39-K1 (PL_DDR_DOT0) | ODT | A4 |

| U39-K3 (PL_DDR_CAS_N) | CAS# | A2 |

| U39-K7 (PL_DDR_CK_N) | CK# | C7 |

| U39-K9 (PL_DDR_CKE_0) | CKE | D9 |

| U39-L2 (PL_DDR_CS_N) | CS# | A5 |

| U39-L3 (PL_DDR_WE_N) | WE# | D8 |

| U39-L7 (PL_DDR_A10) | A10/AP | A3 |

| U39-M2 (PL_DDR_BA0) | BA0 | C4 |

| U39-M3 (PL_DDR_BA2) | BA2 | B1 |

| U39-M7 (PL_DDR_A15) | NC | B5 |

| U39-M8 (VTTVREF_PL) | VREFCA | C8 |

| U39-N2 (PL_DDR_A3) | A3 | B4 |

| U39-N3 (PL_DDR_A0) | A0 | E7 |

| U39-N7 (PL_DDR_A12) | A12/BC# | C2 |

| U39-N8 (PL_DDR_BA1) | BA1 | C3 |

| U39-P2 (PL_DDR_A5) | A5 | G7 |

| U39-P3 (PL_DDR_A2) | A2 | D5 |

| U39-P7 (PL_DDR_A1) | A1 | E6 |

| U39-P8 (PL_DDR_A4) | A4 | B2 |

| U39-R2 (PL_DDR_A7) | A7 | F9 |

| U39-R3 (PL_DDR_A9) | A9 | G5 |

| U39-R7 (PL_DDR_A11) | A11 | E5 |

| U39-R8 (PL_DDR_A6) | A6 | F5 |

| U39-T2 (PL_DDR_RST_N) | RESET# | H14 |

| U39-T3 (PL_DDR_A13) | A13 | J8 |

| U39-T7 (PL_DDR_A14) | A14 | F8 |

| U39-T8 (PL_DDR_A8) | A8 | G6 |

| DDR3引脚(信号名) | 网络名 | PS引脚 |

| U22-B3 (PS_DDR3_DQ3) | DQ0 | G26 |

| U22-B7 (PS_DDR3_DM0) | DM_TDQS | G24 |

| U22-C2 (PS_DDR3_DQ4) | DQ2 | H26 |

| U22-C3 (PS_DDR3_DQS0_P) | DQS | H24 |

| U22-C7 (PS_DDR3_DQ1) | DQ1 | F25 |

| U22-C8 (PS_DDR3_DQ6) | DQ3 | J24 |

| U22-D2 (PS_DDR3_DQ2) | DQ6 | J25 |

| U22-D3 (PS_DDR3_DQS0_N) | DQS_B | G25 |

| U22-E1 (VTTVREF_PS) | VREFDQ | M21 |

| U22-E3 (PS_DDR3_DQ0) | DQ4 | J26 |

| U22-E7 (PS_DDR3_DQ5) | DQ7 | H23 |

| U22-E8 (PS_DDR3_DQ7) | DQ5 | J23 |

| U22-F3 (PS_DDR3_RAS_B) | RAS_B | V23 |

| U22-F7 (PS_DDR3_CLK_P) | CK | R21 |

| U22-G1 (PS_DDR3_ODT) | ODT | Y22 |

| U22-G3 (PS_DDR3_CAS_B) | CAS_B | Y23 |

| U22-G7 (PS_DDR3_CLK_N) | CK_B | P21 |

| U22-G9 (PS_DDR3_CKE) | CKE | U21 |

| U22-H2 (PS_DDR3_CS_B) | CS_B | Y21 |

| U22-H3 (PS_DDR3_WE_B) | WE_B | V22 |

| U22-H7 (PS_DDR3_A10) | A10/AP | M22 |

| U22-J2 (PS_DDR3_BA0) | BA0 | U22 |

| U22-J3 (PS_DDR3_BA2) | BA2 | R22 |

| U22-J8 (VTTVREF_PS) | VREFCA | M21 |

| U22-K2 (PS_DDR3_A3) | A3 | L22 |

| U22-K3 (PS_DDR3_A0) | A0 | K22 |

| U22-K7 (PS_DDR3_A12) | A12/BC_B | P20 |

| U22-K8 (PS_DDR3_BA1) | BA1 | T22 |

| U22-L2 (PS_DDR3_A5) | A5 | N22 |

| U22-L3 (PS_DDR3_A2) | A2 | N21 |

| U22-L7 (PS_DDR3_A1) | A1 | K20 |

| U22-L8 (PS_DDR3_A4) | A4 | M20 |

| U22-M2 (PS_DDR3_A7) | A7 | J21 |

| U22-M3 (PS_DDR3_A9) | A9 | U20 |

| U22-M7 (PS_DDR3_A11) | A11 | H21 |

| U22-M8 (PS_DDR3_A6) | A6 | L20 |

| U22-N2 (PS_DDR3_RESET_B) | RESET_B | H22 |

| U22-N3 (PS_DDR3_A13) | A13 | J20 |

| U22-N7 (PS_DDR3_A14) | A14 | R20 |

| U22-N8 (PS_DDR3_A8) | A8 | T20 |

| U23-B3 (PS_DDR3_DQ3) | DQ0 | M26 |

| U23-B7 (PS_DDR3_DM0) | DM_TDQS | K25 |

| U23-C2 (PS_DDR3_DQ4) | DQ2 | M24 |

| U23-C3 (PS_DDR3_DQS0_P) | DQS | L24 |

| U23-C7 (PS_DDR3_DQ1) | DQ1 | K26 |

| U23-C8 (PS_DDR3_DQ6) | DQ3 | L23 |

| U23-D2 (PS_DDR3_DQ2) | DQ6 | N24 |

| U23-D3 (PS_DDR3_DQS0_N) | DQS_B | L25 |

| U23-E1 (VTTVREF_PS) | VREFDQ | M21 |

| U23-E3 (PS_DDR3_DQ0) | DQ4 | M25 |

| U23-E7 (PS_DDR3_DQ5) | DQ7 | N23 |

| U23-E8 (PS_DDR3_DQ7) | DQ5 | K23 |

| U23-F3 (PS_DDR3_RAS_B) | RAS_B | V23 |

| U23-F7 (PS_DDR3_CLK_P) | CK | R21 |

| U23-G1 (PS_DDR3_ODT) | ODT | Y22 |

| U23-G3 (PS_DDR3_CAS_B) | CAS_B | Y23 |

| U23-G7 (PS_DDR3_CLK_N) | CK_B | P21 |

| U23-G9 (PS_DDR3_CKE) | CKE | U21 |

| U23-H2 (PS_DDR3_CS_B) | CS_B | Y21 |

| U23-H3 (PS_DDR3_WE_B) | WE_B | V22 |

| U23-H7 (PS_DDR3_A10) | A10/AP | M22 |

| U23-J2 (PS_DDR3_BA0) | BA0 | U22 |

| U23-J3 (PS_DDR3_BA2) | BA2 | R22 |

| U23-J8 (VTTVREF_PS) | VREFCA | M21 |

| U23-K2 (PS_DDR3_A3) | A3 | L22 |

| U23-K3 (PS_DDR3_A0) | A0 | K22 |

| U23-K7 (PS_DDR3_A12) | A12/BC_B | P20 |

| U23-K8 (PS_DDR3_BA1) | BA1 | T22 |

| U23-L2 (PS_DDR3_A5) | A5 | N22 |

| U23-L3 (PS_DDR3_A2) | A2 | N21 |

| U23-L7 (PS_DDR3_A1) | A1 | K20 |

| U23-L8 (PS_DDR3_A4) | A4 | M20 |

| U23-M2 (PS_DDR3_A7) | A7 | J21 |

| U23-M3 (PS_DDR3_A9) | A9 | U20 |

| U23-M7 (PS_DDR3_A11) | A11 | H21 |

| U23-M8 (PS_DDR3_A6) | A6 | L20 |

| U23-N2 (PS_DDR3_RESET_B) | RESET_B | H22 |

| U23-N3 (PS_DDR3_A13) | A13 | J20 |

| U23-N7 (PS_DDR3_A14) | A14 | R20 |

| U23-N8 (PS_DDR3_A8) | A8 | T20 |

| U24-B3 (PS_DDR3_DQ3) | DQ0 | T25 |

| U24-B7 (PS_DDR3_DM0) | DM_TDQS | P26 |

| U24-C2 (PS_DDR3_DQ4) | DQ2 | T24 |

| U24-C3 (PS_DDR3_DQS0_P) | DQS | P25 |

| U24-C7 (PS_DDR3_DQ1) | DQ1 | P23 |

| U24-C8 (PS_DDR3_DQ6) | DQ3 | P24 |

| U24-D2 (PS_DDR3_DQ2) | DQ6 | T23 |

| U24-D3 (PS_DDR3_DQS0_N) | DQS_B | R25 |

| U24-E1 (VTTVREF_PS) | VREFDQ | M21 |

| U24-E3 (PS_DDR3_DQ0) | DQ4 | R26 |

| U24-E7 (PS_DDR3_DQ5) | DQ7 | R23 |

| U24-E8 (PS_DDR3_DQ7) | DQ5 | N26 |

| U24-F3 (PS_DDR3_RAS_B) | RAS_B | V23 |

| U24-F7 (PS_DDR3_CLK_P) | CK | R21 |

| U24-G1 (PS_DDR3_ODT) | ODT | Y22 |

| U24-G3 (PS_DDR3_CAS_B) | CAS_B | Y23 |

| U24-G7 (PS_DDR3_CLK_N) | CK_B | P21 |

| U24-G9 (PS_DDR3_CKE) | CKE | U21 |

| U24-H2 (PS_DDR3_CS_B) | CS_B | Y21 |

| U24-H3 (PS_DDR3_WE_B) | WE_B | V22 |

| U24-H7 (PS_DDR3_A10) | A10/AP | M22 |

| U24-J2 (PS_DDR3_BA0) | BA0 | U22 |

| U24-J3 (PS_DDR3_BA2) | BA2 | R22 |

| U24-J8 (VTTVREF_PS) | VREFCA | M21 |

| U24-K2 (PS_DDR3_A3) | A3 | L22 |

| U24-K3 (PS_DDR3_A0) | A0 | K22 |

| U24-K7 (PS_DDR3_A12) | A12/BC_B | P20 |

| U24-K8 (PS_DDR3_BA1) | BA1 | T22 |

| U24-L2 (PS_DDR3_A5) | A5 | N22 |

| U24-L3 (PS_DDR3_A2) | A2 | N21 |

| U24-L7 (PS_DDR3_A1) | A1 | K20 |

| U24-L8 (PS_DDR3_A4) | A4 | M20 |

| U24-M2 (PS_DDR3_A7) | A7 | J21 |

| U24-M3 (PS_DDR3_A9) | A9 | U20 |

| U24-M7 (PS_DDR3_A11) | A11 | H21 |

| U24-M8 (PS_DDR3_A6) | A6 | L20 |

| U24-N2 (PS_DDR3_RESET_B) | RESET_B | H22 |

| U24-N3 (PS_DDR3_A13) | A13 | J20 |

| U24-N7 (PS_DDR3_A14) | A14 | R20 |

| U24-N8 (PS_DDR3_A8) | A8 | T20 |

| U25-B3 (PS_DDR3_DQ3) | DQ0 | V24 |

| U25-B7 (PS_DDR3_DM0) | DM_TDQS | V26 |

| U25-C2 (PS_DDR3_DQ4) | DQ2 | W23 |

| U25-C3 (PS_DDR3_DQS0_P) | DQS | W24 |

| U25-C7 (PS_DDR3_DQ1) | DQ1 | U26 |

| U25-C8 (PS_DDR3_DQ6) | DQ3 | W26 |

| U25-D2 (PS_DDR3_DQ2) | DQ6 | Y25 |

| U25-D3 (PS_DDR3_DQS0_N) | DQS_B | W25 |

| U25-E1 (VTTVREF_PS) | VREFDQ | M21 |

| U25-E3 (PS_DDR3_DQ0) | DQ4 | Y26 |

| U25-E7 (PS_DDR3_DQ5) | DQ7 | U25 |

| U25-E8 (PS_DDR3_DQ7) | DQ5 | U24 |

| U25-F3 (PS_DDR3_RAS_B) | RAS_B | V23 |

| U25-F7 (PS_DDR3_CLK_P) | CK | R21 |

| U25-G1 (PS_DDR3_ODT) | ODT | Y22 |

| U25-G3 (PS_DDR3_CAS_B) | CAS_B | Y23 |

| U25-G7 (PS_DDR3_CLK_N) | CK_B | P21 |

| U25-G9 (PS_DDR3_CKE) | CKE | U21 |

| U25-H2 (PS_DDR3_CS_B) | CS_B | Y21 |

| U25-H3 (PS_DDR3_WE_B) | WE_B | V22 |

| U25-H7 (PS_DDR3_A10) | A10/AP | M22 |

| U25-J2 (PS_DDR3_BA0) | BA0 | U22 |

| U25-J3 (PS_DDR3_BA2) | BA2 | R22 |

| U25-J8 (VTTVREF_PS) | VREFCA | M21 |

| U25-K2 (PS_DDR3_A3) | A3 | L22 |

| U25-K3 (PS_DDR3_A0) | A0 | K22 |

| U25-K7 (PS_DDR3_A12) | A12/BC_B | P20 |

| U25-K8 (PS_DDR3_BA1) | BA1 | T22 |

| U25-L2 (PS_DDR3_A5) | A5 | N22 |

| U25-L3 (PS_DDR3_A2) | A2 | N21 |

| U25-L7 (PS_DDR3_A1) | A1 | K20 |

| U25-L8 (PS_DDR3_A4) | A4 | M20 |

| U25-M2 (PS_DDR3_A7) | A7 | J21 |

| U25-M3 (PS_DDR3_A9) | A9 | U20 |

| U25-M7 (PS_DDR3_A11) | A11 | H21 |

| U25-M8 (PS_DDR3_A6) | A6 | L20 |

| U25-N2 (PS_DDR3_RESET_B) | RESET_B | H22 |

| U25-N3 (PS_DDR3_A13) | A13 | J20 |

| U25-N7 (PS_DDR3_A14) | A14 | R20 |

| U25-N8 (PS_DDR3_A8) | A8 | T20 |

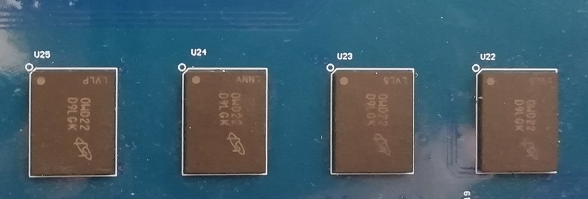

板载一片WM8978,它是带扬声器驱动的立体声多媒体数字信号编译码器。WM8978是一个低功耗、高质量的立体声多媒体数字信号编译码器。它主要应用于便携式应用,比如数码照相机、可携式数码摄像机它结合了立体声差分麦克风的前置放大与扬声器、耳机和差分、立体声线输出的驱动,减少了应用时必需的外部组件,比如不需要单独的麦克风或者耳机的放大器高级的片上数字信号处理功能,包含一个5路均衡功能,一个用于ADC和麦克风或者线路输入之间的混合信号的电平自动控制功能,一个纯粹的录音或者重放的数字限幅功能。WM8978可以被应用为一个主机或者一个从机。基于共同的参考时钟频率,内部的PLL可以为编译码器提供所有需要的音频时钟。此芯片的通信地址固定为7’B0011010。

设计原理图如下:

图17-1 原理图Audio部分

实物图如下

图17-2 音频接口与芯片实物图

引脚分配

| WM8978引脚(引脚名称) | FPGA引脚 |

| 7(LRC) | M8 |

| 8(BCLK) | L8 |

| 9(ADCDAT) | N2 |

| 10(DACDAT) | N2 |

| 11(MCLK) | L7 |

| 16(SCLK) | U9-SC6 |

| 17(SDIN) | U9-SD6 |

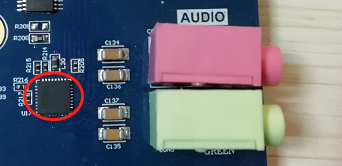

TUSB4041I 器件是一款四端口 USB 2.0 集线器。该器件可在上行端口上提供 USB 高速或全速连接。该器件还可在下行端口上提供 USB 高速、全速或者低速连接。当上行端口连接至仅支持高速、全速和低速连接的电气环境中时,下行端口上的高速、全速和低速 USB 连接被启用。当上行端口被连接到一个只支持全速或低速连接的电气环境中时,下行端口上的 USB 高速连接被禁用。

TUSB4041I 器件能够为包括电池充电支持在内的部分功能提供引脚搭接配置,还能够通过 OTP ROM、I2C EEPROM 或通过 I2C 和 SMBus 从设备接口为 PID、VID 以及自定义端口和物理层配置提供定制支持。使用 I2C EEPROM 或 I2C 和 SMBus 受控接口时,还可以提供定制字串支持。

该器件采用 64 引脚 PAP 封装,工业版的工作温度范围为 -40°C 到 85°C。

原理图请参阅设计原理图。

图18-1 原理图USB部分

图18-2 原理图USB收发器部分

实物图:

图18-3 USB接口实物图

引脚分配:

| USB引脚(信号名) | FPGA引脚 |

| U3-1(CLK_OUT) | K16 |

| U3-2(NXT) | E12 |

| U3-3(DATA0) | K17 |

| U3-4(DATA1) | E22 |

| U3-5(DATA2) | J16 |

| U3-6(DATA3) | D19 |

| U3-7(DATA4) | J18 |

| U3-9(DATA5) | D20 |

| U3-10(DATA6) | D21 |

| U3-13(DATA7) | C21 |

| U3-29(STP) | K19 |

| U3-31(DIR) | E20 |

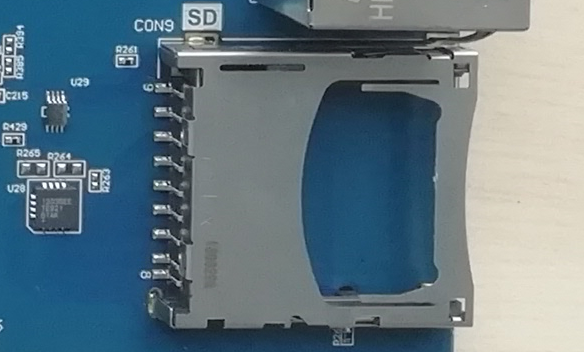

PE7030开发板包含了一个SD卡接口,以提供用户访问SD卡存储器,用于存储ZYNQ芯片的BOOT程序, Linux操作系统内核, 文件系统以及其它的用户数据文件。SDIO信号与ZYNQ的PS BANK501的IO信号相连,因为该BANK的VCCMIO设置为1.8V,但SD卡的数据电平为3.3V,这里通过TXS0102和MAX13035E电平转换器来连接。 Zynq7000 PS和SD卡连接器的原理图如图19-1至19-3所示。

图19-1 SDcard原理图部分

图19-2 原理图MAX13035E电平转换芯片部分

图19-3 原理图TXS0102电平转换芯片部分

实物图:

图19-4 SDcard实物图

引脚分配:

| 信号名称 | ZYNQ引脚名 | ZYNQ引脚号 | 备注 |

| SDIO_CD_DAT3 | PS_MIO45 | C18 | SD卡插入信号 |

| SDIO_CMD | PS_MIO41 | C19 | SD命令信号 |

| SDIO_CLK | PS_MIO40 | C22 | SD时钟信号 |

| SDIO_DAT0 | PS_MIO42 | F17 | SD数据Data0 |

| SDIO_DAT1 | PS_MIO43 | D18 | SD数据Data1 |

| SDIO_DAT2 | PS_MIO44 | E18 | SD数据Data2 |

| SDIO_SDDET | PS_MIO48 | B21 | |

| SDIO_SDWP | PS_MIO49 | A18 |

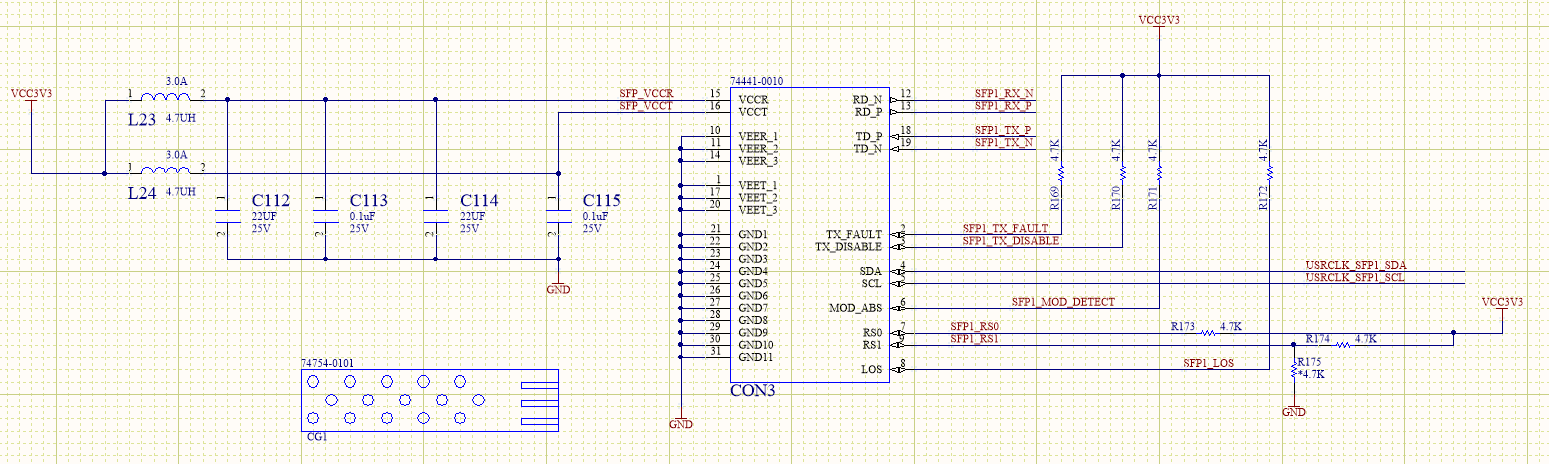

实物图:

图20-1 光纤接口

图20-2 原理图光纤部分

引脚分配

| 引脚(信号名) | FPGA引脚 |

| Con3-12(SFP1-RX-N) | T3 |

| Con3-13(SFP1-RX-P) | T4 |

| Con3-18(SFP1-TX-P) | R2 |

| Con3-19(SFP1-TX-N) | R1 |

| Con4-12(SFP1-RX-N) | V4 |

| Con4-13(SFP1-RX-P) | V3 |

| Con4-18(SFP1-TX-P) | U2 |

| Con4-19(SFP1-TX-N) | U1 |